جمع کننده کامل 1 بیتی زیر آستانه ای در فناوری تراشه هاى نیمه هادى اکسید فلزى تکمیلى65 نانومتری Bit Sub Threshold Full Adders in 65nm CMOS Technology

Abstract

In this paper a new full adder (FA) circuit optimized for ultra low power operation is proposed. The circuit is based on modified XOR gates operated in the subthreshold region to minimize the power consumption. Simulated results using 65nm standarad CMOS models are provided. The simulation results show a 5% - 20% for frequency ranges from 1 KHz to 20MHz and supply voltages lower than 0.3V.

Keywords: Full adder, ultra low power, subthreshold

چکیده فارسی

در این مقاله، جمع کننده کامل (FA) نوینی ارائه میگردد که برای عملکرد با توانهای بسیار پایین بهینه سازی شده است. مدار مذکور، بر پایه گیتهای XOR اصلاح شدهای طراحی گشته که با هدف کمینه سازی مصرف توان در ناحیه زیرآستانهای عمل می کنند. نتایج شبیه سازی شده با مدلهای استاندارد CMOS 65 نانومتر انجام شده است. نتایج شبیه سازی، یک بهبود 5 تا 20 درصدی را در بازه فرکانسی 1Khz تا 20MHz و ولتاژهای تغذیه زیر 0.3V نشان میدهد.

مشخصات

توسط: Farshad Moradi and others مجله: International Conference on Microelectronics سال انتشار: 2008 میلادی تعداد صفحات متن اصلی: 4 تعداد صفحات متن ترجمه: 11 تاریخ درج: ۱۳۹۷/۵/۲۸ منبع: دیتاسرا

خرید آنلاین فایل ترجمه

عنوان: جمع کننده کامل 1 بیتی زیر آستانه ای در فناوری تراشه هاى نیمه هادى اکسید فلزى تکمیلى65 نانومتری حجم: 891.81 کیلوبایت فرمت فایل: pdf قیمت: 99500 تومان رمز فایل (در صورت نیاز): www.datasara.com نرم افزارهای مورد نیاز: winrar - adobe acrobat - office

تنها با ارسال یک ایمیل وجه خود را دریافت نمایید

دانلود فایل اصلی

عنوان: Bit Sub Threshold Full Adders in 65nm CMOS Technology

مقدمه

تغییر مقیاس ولتاژ تغذیه یکی از موثرترین راهها در کاهش مصرف توان مدارهای دیجیتال است.کارایی این روش بعلتوجود رابطه درجه دوم میان مصرف توان دینامیک و ولتاژ تغذیه می باشد. اما در این روش، عملکرد مدار به خاطر رابطه معکوس تاخیر مدار با سطح جریان کاهش می یابد. به همین علت، ولتاژ آستانه را در فرایندهای زیرمیکرونی عمیق برای رفع این مشکل کاهش می دهند. کاهش ولتاژ آستانه، منجر به افزایش نمایی جریان زیرآستانه میگردد که امکان استفاده از این ناحیه (زیرآستانه) را در مدارهای منطقی ارزیابی - با کران نویز قابل قبول - می دهد. بدون اعمال روشهای خاص، عملکرد زیرآستانه ای سبب کاهش سرعت پاسخگویی (به سبب کاهش جریان) می شود. جریان مورد ارزیابی در این حالت، جریانی است که در ولتاژ گیت –سورس کوچکتر یا مساوی ولتاژ آستانه و ولتاژ تغذیه نزدیک به ولتاژ آستانه رخ می دهد. همانطور که در شکل 1 مشاهده می شود، نسبت I_on (وقتی ترانزیستور در حال ارزیابی است) به I_off (وقتی ولتاژ گیت-سورس صفر یا نزدیک صفر است) در مقایسه با Ion/Ioff در ولتاژهای تغذیهی بالا،کوچکتر است. با این حال، در کاربردهای با مصرف توان بسیار پایین (مثل ایمپلنتها یا حسگرهای بدون سیم)، سرعت کاری دغدغه اصلی طراحی نیست، زیرا قیود پهنای باندی در این موارد با مسامحه اعمال می گردد. برای این کاربردها، مهمترین هدف طراحی بهینه سازی بمنظور مصرف توان پایین است. جمع دو بیت A و B با بیت نقلی Cin، بیت SUM (مجموع) و بیت خروجی نقلی Cout را تولید میکند. روابط زیر عملکرد جمع کننده کامل را شرح می دهد:

-1- SUM=A⨁B⨁C_in

-2- C_out=(A∙B)+(A⋅C_in )+(B∙C_in)

-3- H=A⨁B

-4- SUM=H⨁C_in

-5- C_out=A⋅H^'+C_in∙H

طراحی اغلب جمع کننده ها بر پایهی 2 گیت XOR (یکی برای ایجاد H و H’ و دیگری برای ایجاد خروجی SUM) و یک مولتی پلکسر (MUX) برای ایجاد Cout [1] می باشد. در [1] توپولوژی های مختلف مداری در گستره ی مختلفی از ولتاژ تغذیه بررسی شده است. در این مقاله،نشان داده شد که مدارهای گزارش شده در ولتاژهای تغذیه بسیار پایین عمل نمیکنند. تاخیر در مدارهای مذکوردر ولتاژهای تغذیه پایین، به خاطر کاهش جریان مورد ارزیابیِ شارژ یا تخلیه کننده، بالا می باشند. کاهش جریان ارزیابی، تاخیر مدار را افزایش می دهد که به نوبه خود ماکزیمم فرکانس قابل اعمال را کاهش می دهد. اغلب مدارهای مورد بررسی در [1] برای کاربردهای سرعت بالا و مقیاس کوچک و با فناوریهای زیر 0.18 میکرون مورد استفاده قرار می گیرند، و در ولتاژهای تغذیه زیر 0. 2 ولت در فناوری 65 نانومتری CMOS، به خاطر سازوکارهای نشتی مختص فناوریهای مقیاس نانو بدرستیعمل نمیکنند.

شکل 1: نسبت Ion/Ioff برای تجهیزات NMOS

توپولوژی مداری دیگر برای جمع کننده، جمع کننده کامل بازیابی انرژی استاتیک (SERF) است که در شکل 2 نشان داده شده است. این توپولوژی فقط از 10 ترانزیستور استفاده می کند که کمترین تعداد ترانزیستورهای گزارش شده تا بحال است. طبق اظهارات [2] همچنین عنوان شده است که SERF از نظر مصرف توان نیز حداقل مصرف توان را دارد. البته در ولتاژهای تغذیه پایین، مدار در حالت A=1 و B=1 و Cin=0 دچار مشکل می شود. در این حالت، Cout توسط یک ترانزیستور گذر NMOS به سطح HIGH می رود؛ اما از آنجا که اینکه توسط ترانزیستور NMOS به VDD متصل است - و همچنین به گیت ترانزسیتور گذر NMOS در این حالت به VDD-Vth وصل است -نمی تواند تا سطح VDD شارژ شود. بنابراین Cout فقط می تواند تا VDD-2Vth بالا بیاید که محدودیتیرا برای کار با ولتاژهای تغذیه بسیار پایین ایجاد می کند. بعنوان مثال فرض کنیدVth برای ترانزیستور NMOSدر 65 نانومتر برابر با 0.18 V باشد؛ بنابراین برای جلوگیری از خطا در این ورودی هاCout می تواند تا VDD-0.36 بالا رود. پس ولتاژ تغذیه باید بالاتر از 0.72 باشد. البته این به اندازه ترانزیستور هم بستگی دارد: با ترانزیستورهای بزرگتر، میتوانیم ولتاژ تغذیه را بیشتر کاهش دهیم. VDDبرای تولیدHIGH منطقی در خروجی، باید از Cout بزرگتر باشد. اما استفاده از NMOS برای شارژ کردن Cout به سطحHIGH، موجب می شود مدار در بعضی از ورودی ها بدرستی عمل نکند، و وقتی عملکرد برای ما ارجح باشد، این امر بسیار مسئله ساز است. در [3] یک جمع کننده کامل 14 ترانزیستوری ارائه شده است. مدارهای ارائه شده همگی جزو طراحی های کم مصرف حساب می شوند، اما در توانهای بسیار پایین، وقتی ولتاژ تغذیه به زیر ولتاژ آستانه کاهس می یابد، بدرستی عمل نمی کنند. بعضی از آنها از نظر مساحت/سطح، بهینه تر از مدارهای استاندارد طراحی شده اند [4]، اما به هنگام تغییر حالت/وضعیت سگینالهای ورودی، افت ولتاژ در آنهاامری حتمی است. از طرفی، برای ارزیابی این مدارها، باید اندازه ترانزیستورها افزایش یابد، که موجب افزایش مصرف توان می گردد. مرجع [5] ، پیکره بندی های متفاوتی از طراحی جمع کننده کامل در ناحیه زیرآستانه ای ارائه می دهد. با این حال، این مدارها هم دارای overhead سطحی کمی هستند و در فناوری های زیرمیکرون بسیار عمیق بدرستی کار/عمل نمی کنند.

شکل 2: جمع کننده کامل 1 بیتی SERF [2]

همانطور که رابطه (1) نشان می دهد، سیگنال SUM را می توان با استفاده از دو گیت XOR ایجاد کرد. خروجی XOR اول، سیگنال H است که برای تولیدCout استفاده می شود [6]. بدین ترتیب برای تولید سیگنال H و SUM، از گیتهای XOR استفاده می کنیم و برای تولیدCOUT از H، از یک MUX-2X1 کوچک استفاده می کنیم. بنابراین می توان دید مهمترین و غالب ترین بخش مدار جمع کننده کامل، گیت XOR آن است. پس با طراحی گیت XOR بسیار کم توان، می توان یک جمع کننده کامل بسیار کم توان ساخت. در بخشی که در ادامه می آید، توپولوژیهای مختلف مدار گیت XOR بررسی می شود و سپس مدارهای پیشنهاد شده در این مقاله ارائه/معرفی می شود.

در بخش مقدمه، هدف مقاله به همراه بررسی مدارهای ارائه شده تابحال برای جمع کننده کامل تشریح شد. در بخش 2، عضو اصلی ساختار جمع کننده کامل، یعنی گیت XOR کم توان تشریح، تحلیل و شبیه سازی می شود. همچنین این بخش توپولوژی گیت XORکم توان را برای ولتاژهای تغذیه بسیار پایین در فناوریهای زیرمیکرونی عمیق، بهمراه نتایج شبیه سازی برای گیت های XORتشریح می کند. در بخش 3، طراحی FA 1 بیتی، با استفاده از گیت های XOR پیشنهادی توضیح داده می شود. نهایتا جمعبندی و نتیجه گیری در بخش 4 آورده شده است.

مدار XOR پیشنهادی

شکل 3، یک گیت XOR-XNORبرای کاربردهای بسیار کم توان را نشان می دهد [5]. این گیت مصرف توان بسیار پایینی دارد و جریان نشتی آن نیز کم است، اما در هنگام تغییر وضعیت، خروجیهای آن دچار افت ولتاژ می گردند. مشکل دیگر این مدار اضافه سطح بالای آنست؛ چون 16 ترانزیستور در این مدار به کار رفته است. در مقیاس نانومتری، و در ولتاژ زیرآستانه این مدار به علت وجود ترانزیستورهای NMOS نشت کننده نمی تواند به درستی عمل کند.

شکل 3: مدار گیت XOR-XNOR [5].

افت ولتاژ نامطلوب، در زمان تاخیر معکوسکننده هنگام تولید سیگنالهای B’ و A’، رخ می دهد. نویسنده برای حل مشکل مسیرهای نشتی در این مدار، از ترانزیستورهای چندآستانه ای ولتاژ بعنوان راه حل مناسب ولی پرهزینه (به خاطر نیاز به گزینه های پردازشی بیشتر) استفاده کرده است. مدارهای گیت XOR دیگر نیز در [4] ارائه شده اند. شکل 4 گیت XOR استاندارد را با استفاده از منطق CMOS استاتیک و ترانزیستور گذر نشان می دهد. مشکلات مرتبط با این مدارها در [3] شرح داده شده است.

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

برای حل مشکل میسرهای نشتی در هنگام تغییر وضعیت از AB = 01 به AB=10 ، از یک گیت XORاستفاده می کنیم(نشان داده شده در شکل 5). جریان نشتی موقعی بوجود می آید که جریان idle عناصر موازی موجب کاهش Ion/Ioff می گردد. نمونه ای از یک مسیر نشتی در گیت XOR نشان داده شده است: شکل 5-الف و5-ب، شماتیک گیت XOR کوچک را نشان می دهند [4]که در طراحی سنتی مدار معمولا به کار می رود. تحلیل جریانهای drive و جریانهای نشتی برای بردار ورودی A=0,B=1 نشان می دهد چون سه عنصر "خاموش" و یک عنصر "روشن" در این وضعیت واقعند، Ion/Ioff کاهش می یابد. شبیه سازی نشان می دهد که ولتاژ خروجی تاVddبالا می رود؛ اما در هنگام تغییر وضعیت، افت ولتاژی در خروجی رخ می دهد که در ولتاژهای تغذیه زیر 0.2 V موجب عملکرد نادرست می گردد. اگر نغییرات فرایند نیز در تحلیل مدنظر قرار گیرد، این مشکل پیچیده تر می شود.

شکل 5: رفتار XOR در هنگام تغییر وضعیت از AB=10 به AB=01

شکل 6 مدار گیت XORتشریح شده در [3] را در وضعیت A=0, B=1 نشان می دهد. رفتار این مدار در زمان تغییر وضعیت از AB=01 به AB=10 مورد تحلیل قرار گرفته است. همانطور که مشخص است، در هنگام تغییر وضعیت (در طول مدت تاخیر معکوس کننده)، یک ترانزیستور PMOS روشن بوده و سعی در بالا بردن سطح گره خروجی دارد. از طرف دیگر یک ترانزیستور NMOSمی خواهد گره خروجی را به سمت صفر ببرد که باعث افت ولتاژ در خروجی می گردد. همچنین همانطور که دیده می شود، در یکی از ترانزیستورهای PMOS جریان ضعیفی حاضر است که به مسیرهای تخلیهولتاژ اضافه می کند. البته، زمان تخلیهولتاژ به کوتاهی زمان تاخیر معکوس کننده است.پس از این زمان، در وضعیت X، یک مسیر زیرآستانه ای جریان را از گره خروجی سینک می کند؛ و این در حالی است که ترانزیستور PMOS سمت راستی سعی در حفظ وضعیت خروجی دارد. برای حل این مشکل، روشی برای حذف اثر تخلیه در گره خروجی در هنگام تغییر وضعیت ارائه می دهیم. برای حذف مسیر تخلیه در هنگام تغییر وضعیت، سیگنال ورودی Bرا بعد از تاخیری معادل با تاخیر دو معکوس کننده اعمال می کنیم. بدین ترتیب رفتار مدار در مقایسه با مدار اصلی بهبود می یابد. همانطور که در شکل 6 دیده می شود، یک ترانزیستور NMOS در این وضعیت روشن است و یک ترانزیستور در ناحیه زیرآستانه ای است (VGS=0 , VDS=VDD) . در نتیجه جریانهایی که شروع به تخلیه کردن سطح ولتاژ وضعیت گره خروجی می کنند، تقریبا نصف جریانهای متناظر در مدار اصلی خواهند بود. این کاهش توان، با یک مصالحه در افزایش مساحت مدار و افزودن یک معکوس کننده اضافی صورت می گیرد. با این حال، چون مصرف توان مدار پیشنهادی بیش از 20% در مقایسه با مدار اصلی کاهش می یابد، برای کاربردهایی که در ان مصرف توان دغدغه اصلی این اضافه سطح قابل قبول است. علاوه بر آن میزان مصونیت از نویز مدار نیز بهبود می یابد.

شکل 6: عملکرد گیت XOR

شماتیک مدارهای جمع کننده پیشنهادی، در شکل 7 نشان داده شده اند. این مدارها با اسامی AP و BP و CP و DP مشخص شده اند. در مدار BP، سیگنال ورودی B بعد از تاخیری معادل با تاخیر دو معکوس کنده اعمال می شود. در مدار DP، معکوس کننده دوم از معکوس کننده اول بزرگتر است. ایده دیگری که شکل سیگنال را در خروجی بهبود می بخشد و همچنین مصرف توان را کاهش می دهد (ولی سرعت پاسخ را کاهش می دهد)، مدار AP نشان داده شده در شکل 7 است. این مدار از اثر stack برای حذف مسیرهای نشتی که منجر به افت ولتاژ در نقطه تغییر وضعیت (سویچینگ) می شود استفاده می کند.

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

Bit Sub Threshold Full Adders in 65nm CMOS Technology

جمع کننده کامل 1 بیتی زیر آستانه ای در فناوری تراشه هاى نیمه هادى اکسید فلزى تکمیلى65 نانومتری

Bit Sub Threshold

Full Adders in

65nm CMOS Technology

جمع کننده کامل

1 بیتی زیر

آستانه ای در

فناوری تراشه هاى

نیمه هادى اکسید

فلزى تکمیلى65 نانومتری

دستورالعمل طراحی و محاسبه سیستم روشنایی

.png)

.png)

مجموعه دستورالعمل های ارائه شده در دیتاسرا شامل ضوابط و مراحل تحلیل و طراحی سازه های گوناگون صنعتی و بر اساس الزامات مندرج در آیین نامه های معتبر داخلی و ... [ ادامه مطلب ]

قیمت: 119500 تومان

مشخصات کلی:

قیمت: 119500 تومان

مشخصات کلی:

صفحات متن اصلی: 30

گروه:

دستورالعمل طراحی

قیمت: 119500 تومان

قیمت: 119500 تومان

صفحات متن اصلی: 30

گروه: دستورالعمل طراحی

تقویت کننده ی شبه تفاضلی کلاس-AB برمبنای اینورتر CMOS برای کاربردهای HF

.png)

.png)

Abstract This paper presents a CMOS inverter-based c1ass-AB pseudo differential amplifier for HF applications using new sim pIe rail-to-rail CMFB circuit. The proposed circuit em ploys two CMOS inverters and the ... [ ادامه مطلب ]

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

روش جاروب رو به عقب، برای حل پخش بار در شبکه های توزیع

.png)

.png)

Abstract A methodology for the analysis of radial or weakly meshed distribution systems supplying voltage dependent loads is here developed. The solution process is iterative and, at each step, loads are ... [ ادامه مطلب ]

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

بازسازی سه بعدی و تشخیص چهره با استفاده از ICA مبتنی بر هسته و شبکه های عصبی

.png)

.png)

Abstract Kernel-based nonlinear characteristic extraction and classification algorithms are popular new research directions in machine learning. In this paper, we propose an improved photometric stereo scheme based on improved kernel-independent component ... [ ادامه مطلب ]

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

جمع کننده کامل 1 بیتی زیر آستانه ای در فناوری تراشه هاى نیمه هادى اکسید فلزى تکمیلى65 نانومتری

.png)

.png)

Abstract In this paper a new full adder (FA) circuit optimized for ultra low power operation is proposed. The circuit is based on modified XOR gates operated in the subthreshold region ... [ ادامه مطلب ]

قیمت: 99500 تومان

قیمت: 99500 تومان

قیمت: 99500 تومان

قیمت: 99500 تومان

تغذیه کشتی توسط مولد قرار گرفته در خشکی (Cold Ironing)

مجله in detail (شماره 2، 2017): تصمیمیکه توسط اسطوره سینمای هالیوود "آرنولد شوارتزنگر" در سال 2006 بعنوان فرماندار ایالت کالیفرنیا گرفته شد، تأثیر چشمگیری بر تجارت شرکت وارتسیلا داشت. وی دستور داد تا به منظور کاهش آلودگی هوا و انتشار گازهای گلخانه ای، سواحل ایالت کالیفرنیا به سیستم برق رسانی از خشکی به کشتی (Cold ironing) مجهز شوند. این تصمیم باعث ... [ ادامه مطلب ]

تولید برق از امواج دریا (Catching the Surge)

مجله in detail (شماره 2، 2017): در ماه سپتامبر وارتسیلا اعلام نمود که با شرکت AW-Energy جهت تولید برق از امواج دریا همکاری خواهد نمود. تکیه گاه یاتاقان های فلزی، یاتاقانهای کامپوزیتی، محفظه های آب بند لبه ای و کوپلینگ های هیدرولیک مورد استفاده در اولین WaveRoller مقیاس واقعی شرکت AW Energy، توسط وارتسیلا فراهم شده است. تجهیزات مورد استفاده در ... [ ادامه مطلب ]

برق رسانی به شبکه های ایزوله (Powering Isolated Grids)

مجله in detail (شماره 2، 2017): مجله in detail (شماره 2، 2017): این مطلب به مطالعه بر روی یک نیروگاه برق هیبریدی (مرکب) وارتسیلا (موتورهای احتراق داخلی و ذخیره کننده های انرژی) و ارزش افزوده ای که میتواند در اثر صرفه جویی اقتصادی و بالا بردن راندمان برای صاحبان و بهره برداران آن بهمراه داشته باشد میپردازد. نیروگاه هیبریدی مورد مطالعه مشتمل بر ... [ ادامه مطلب ]

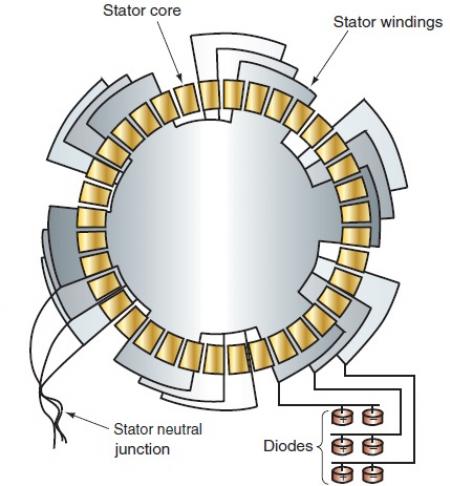

تشخیص خطای سیم بندی استاتور با آنالیز موجک و شبکه عصبی (Stator Winding Fault Diagnosis Based On Wavelet Transformation and BP Neural Network)

.png)

.png)

چکیده: در این پایان نامه ابتدا عیوب الکتریکی و مکانیکی در ماشینهای الکتریکی بررسی گردیده و عوامل به وجود آورنده و روشهای رفع این عیوب بیان شده است . به ... [ ادامه مطلب ]

قیمت: 119500 تومان

مشخصات کلی:

قیمت: 119500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 119500 تومان

قیمت: 119500 تومان

گروه: دستورالعمل طراحی

اثر wake در مکان یابی بهینه توربین های بادی یک مزرعه بادی

.png)

.png)

چکیده: افزایش روز افزون مزارع توربین بادی و گسترش آن ها، ضرورت روش هایی برای بهینه سازی مسائل فنی و اقتصادی آن ها را بیش از پیش نمایان می سازد. یکی از چا لش های پیش رو برای طراحی مزارع بادی تعیین موقعیت توربین ها نسبت به یکدیگر می باشد. این مقاله روشی را برای بهینه سازی چیدمان توربین ها در یک ... [ ادامه مطلب ]

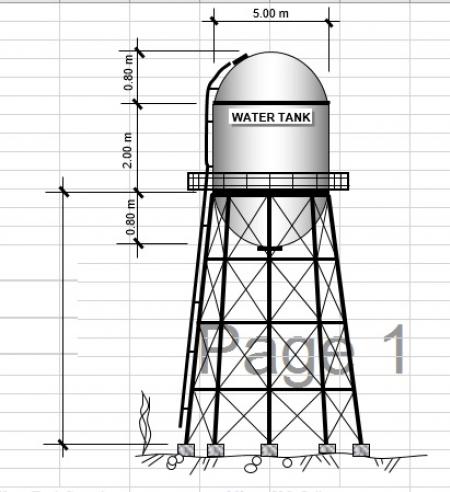

فایل اکسل طراحی مخزن فلزی هوایی بر اساس آیین نامه AISC با در نظر گرفتن نیروی باد و زلرله

.png)

.png)

فایل پیش رو اکسل طراحی مخزن فلزی هوایی می باشد که بر اساس آیین نامه AISC و با در نظر گرفتن نیروی باد و زلرله محاسبات را انجام داده و ... [ ادامه مطلب ]

قیمت: 79500 تومان

مشخصات کلی:

قیمت: 79500 تومان

مشخصات کلی:

گروه:

اکسل طراحی

قیمت: 79500 تومان

قیمت: 79500 تومان

گروه: اکسل طراحی

فایل اکسل تحلیل اتصال برشی دارای خروج از مرکزیت برای گروه پیچ

.png)

.png)

این برنامه ظرفیت برشی اتصال پیچ و مهره ای دارای خروج از مرکزیت برای گروه پیچ را محاسبه می کند، ابزاری مناسب برای طراحی صفحات gusset و اتصالات پیچ و ... [ ادامه مطلب ]

قیمت: 79500 تومان

مشخصات کلی:

قیمت: 79500 تومان

مشخصات کلی:

گروه:

اکسل طراحی

قیمت: 79500 تومان

قیمت: 79500 تومان

گروه: اکسل طراحی

فایل اکسل طراحی روسازی آسفالتی بر مبنای آیین نامه آشتو و استفاده از آزمایش ظرفیت باربری کالیفرنیا

.png)

.png)

فایل پیش رو اکسل طراحی روسازی آسفالتی بر مبنای آیین نامه آشتو می باشد که با استفاده از نتایج آزمایش ظرفیت باربری کالیفرنیا CBR اطلاعات ورودی را تحلیل و نتایج را ... [ ادامه مطلب ]

قیمت: 79500 تومان

مشخصات کلی:

قیمت: 79500 تومان

مشخصات کلی:

گروه:

اکسل طراحی

قیمت: 79500 تومان

قیمت: 79500 تومان

گروه: اکسل طراحی

دستورالعمل طراحی ابعاد و سازه شالوده های عمیق (شمع ها و پایه های عمیق) در خشکی

.png)

.png)

مجموعه دستورالعمل های ارائه شده در دیتاسرا شامل ضوابط و مراحل تحلیل و طراحی سازه های گوناگون صنعتی و بر اساس الزامات مندرج در آیین نامه های معتبر داخلی و ... [ ادامه مطلب ]

قیمت: 119500 تومان

مشخصات کلی:

قیمت: 119500 تومان

مشخصات کلی:

صفحات متن اصلی: 27

گروه:

اکسل طراحی

قیمت: 119500 تومان

قیمت: 119500 تومان

صفحات متن اصلی: 27

گروه: اکسل طراحی

تحلیل غیرخطی و مدل سازی عددی تیر بتن مسلح تقویت شده با FRP توسط Finite Element Method

.png)

.png)

"پایان نامه مهندسی عمران مقطع کارشناسی ارشد - گرایش سازه" تحلیل غیرخطی و مدل سازی عددی تیر بتن مسلح تقویت شده با FRP توسط Finite Element Method مشخصات کلی: شامل فایلهای word و ... [ ادامه مطلب ]

قیمت: 129500 تومان

مشخصات کلی:

قیمت: 129500 تومان

مشخصات کلی:

گروه:

اکسل طراحی

قیمت: 129500 تومان

قیمت: 129500 تومان

گروه: اکسل طراحی

بررسی پارامترهای هندسی مهاربند زانویی

.png)

.png)

"پروژه دانشجویی مهندسی عمران" بررسی پارامترهای هندسی مهاربند زانویی مشخصات کلی: شامل فایلهای word و pdf بالغ بر 146 صفحه (4 فصل) فهرست مطالب فصل اول 1-1- مقدمه 1-2- شکل پذیری سازه ها 1-3- مفصل و لنگر پلاستیک 1-4- منحنی ... [ ادامه مطلب ]

قیمت: 129500 تومان

مشخصات کلی:

قیمت: 129500 تومان

مشخصات کلی:

گروه:

اکسل طراحی

قیمت: 129500 تومان

قیمت: 129500 تومان

گروه: اکسل طراحی

تحلیل و طراحی سیستم گرمایشی ساختمان مسکونی با استفاده از ذخیره کننده های حرارتی PCM

.png)

.png)

"پایان نامه مهندسی مکانیک مقطع کارشناسی ارشد - گرایش تبدیل انرژی" تحلیل و طراحی سیستم گرمایشی ساختمان مسکونی با استفاده از ذخیره کننده های حرارتی PCM تهیه شده بصورت کاملا انحصاری توسط ... [ ادامه مطلب ]

قیمت: 449000 تومان

مشخصات کلی:

قیمت: 449000 تومان

مشخصات کلی:

گروه:

اکسل طراحی

قیمت: 449000 تومان

قیمت: 449000 تومان

گروه: اکسل طراحی

شناسایی و رتبه بندی دلایل انحراف از هزینه پیش بینی شده و ارائه راهکارهای کاهش آن: مطالعه موردی پروژه های "پتروشیمی الف"

.png)

.png)

"پایان نامه مهندسی عمران مقطع کارشناسی ارشد - گرایش مهندسی و مدیریت ساخت" شناسایی و رتبه بندی دلایل انحراف از هزینه پیش بینی شده و ارائه راهکارهای کاهش آن: مطالعه ... [ ادامه مطلب ]

قیمت: 259500 تومان

مشخصات کلی:

قیمت: 259500 تومان

مشخصات کلی:

گروه:

اکسل طراحی

قیمت: 259500 تومان

قیمت: 259500 تومان

گروه: اکسل طراحی

مکانیک شکست (Fracture Mechanics)

.png)

.png)

مقدمه : یکی از عمده ترین مسائلی که انسان از زمان ساختن سادهترین ابزارها با آن مواجه بوده است پدیده شکست در اجسام میباشد و درواقع برای استفاده از مواد ... [ ادامه مطلب ]

قیمت: 99500 تومان

مشخصات کلی:

قیمت: 99500 تومان

مشخصات کلی:

گروه:

اکسل طراحی

قیمت: 99500 تومان

قیمت: 99500 تومان

گروه: اکسل طراحی

فایل اکسل جامع طراحی دیوار حائل (با در نظر گرفتن نیروی زلزله)

.png)

.png)

فایل اکسل طراحی دیوار حائل (با در نظر گرفتن نیروی زلزله) دیوار حائل یا سازه نگهبان بنایی است که به منظور تحمل بارهای جانبی ناشی از خاکریز پشت دیوار، سازه مجاور، ... [ ادامه مطلب ]

قیمت: 119500 تومان

مشخصات کلی:

قیمت: 119500 تومان

مشخصات کلی:

گروه:

اکسل طراحی

قیمت: 119500 تومان

قیمت: 119500 تومان

گروه: اکسل طراحی

.png)