طراحی هسته میکروکنترلر کامپیوتر مجموعه دستورالعمل هاى کاسته شده در 48 ساعت Design of a RISC Microcontroller Core in 48 Hours

Abstract

In this paper we present a design case study using Handel-C—a recently developed programming language for compilation of high-level programs directly into FPGA hardware. The design is an 8-bit RISC microcontroller core with 33 instructions, prescaler and a programmable timer. Handel-C was used throughout the entire design and debugging flow. The RISC microcontroller design was implemented in on the XESS XS40 FPGA board with Xilinx XC4010XL FPGA . The overall design, including debugging, testing and the FPGA implementation was completed in less than 48 man-hours.

چکیده فارسی

در این مقاله مطالعه موردی، طرحی با استفاده از هندل C –- زبان برنامه نویسی که اخیراً برای کامپایل برنامه های سطح بالا به طور مستقیم در سخت افزارFPGA توسعه یافته است - ارائه می نماییم. این طرح یک هسته میکروکنترلر RISC هشت بیتی با 33 دستورالعمل، پرسی کالر (Prescaler) و یک تایمر قابل برنامه ریزی می باشد. هندل-C در کل طراحی و جریان اشکال زدایی مورد استفاده قرار گرفت. طرح میکروکنترلر RISC توسط Xilinx XC4010XL FPGA در صفحه مدار XESS XS40 FPGA اجرا شد. طرح کلی، از جمله اشکال زدایی، تست و پیاده سازی FPGA در کمتر از 48 ساعت به پایان رسید.

مشخصات

توسط: D. Sulik, M.Vasilko, D.urackova تعداد صفحات متن اصلی: 11 تعداد صفحات متن ترجمه: 18 تاریخ درج: ۱۳۹۵/۷/۷ منبع: دیتاسرا

خرید آنلاین فایل ترجمه

عنوان: طراحی هسته میکروکنترلر کامپیوتر مجموعه دستورالعمل هاى کاسته شده در 48 ساعت حجم: 65.70 کیلوبایت فرمت فایل: pdf قیمت: 119500 تومان رمز فایل (در صورت نیاز): www.datasara.com نرم افزارهای مورد نیاز: winrar - adobe acrobat - office

تنها با ارسال یک ایمیل وجه خود را دریافت نمایید

دانلود فایل اصلی

عنوان: Design of a RISC Microcontroller Core in 48 Hours

. مقدمه

افزایش ظرفیت عملکرد و گیت دستگاه های FPGA اجازه می دهد تا سیستم های منطقی پیچیده در یک دستگاه واحد قابل برنامه ریزی اجرا شود. این پیچیدگی در حال رشد خواستار روش های طراحی می باشد که بتواند با طرح های حاوی صدها هزار گیت منطقی، حافظه، رابط سرعت بالا و مولفه های دیگر با عملکرد بالا از عهده آن برآید. روش های طراحی مبتنی بر زبان های مشتق شده از زبان های برنامه نویسی سنتی از قبیل C ، پاسکال، جاوا و مابقی یک گروه از چنین رویکردهای طراحی می باشد. این زبان های برنامه نویسی به طراحان اجازه می دهند تا از قوانین گرامری زبان آشنا برای توسعه سیستم های سخت افزاری سطح بالا استفاده نمایند.

در این مقاله، مطالعه موردی از طراحی هسته میکروکنترلر RISC را ارائه می نماییم که با استفاده از جریان طراحی کامپایل سخت افزار طراحی شده است. زبانی مانندC به اصطلاح زبان هندل-C برای طراحی سخت افزاری مورد استفاده قرار می گیرد. هدف از این کار ، ارزیابی امکان استفاده از هندل-C برای طراحی سریع و نمونه سازی ریزپردازنده بود.

در بخش 2 ساختار میکروکنترلر RISC اجرا شده در این مطالعه موردی را بطور مطرح می نماییم. بخش 3 جزئیات روش پیاده سازی، از جمله نمونه های واقعی از برنامه هندل -C مورد استفاده در طراحی و جزئیات کلی پروژه را بیان می نماید . این مقاله با خلاصه وضعیتی در بخش 4 نتیجه گیری می شود.

2. ساختار طراحی

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

شکل 1 . ساختار هسته میکروکنترلر RISC

هسته پردازندهRISC توسط رجیستر در حال کار با Xیک ALU 8 بیتی ارائه می نمایدALU از عملیات محاسباتی ساده، از جمله جمع، تفریق، جابه جایی و عملیات منطقی بولی پشتیبانی کی نماید. رجیستر X یک رجیستر در حال کار 8 بیتی می باشد که توسط عملیات ALU مورد استفاده قرار گرفته است. ALU نیز تعدادی پرچم ارائه می نماید تا شرایط مختلف پس از انجام عملیات محاسباتی را نشان دهد. علامت های نشان داده شده توسط پرچم های شامل Carry، Digit Carry و Zero می باشد.

یک تایمر 8 بیتی (TMR0) و یک ماژول پرسی کالر 8 بیتی به عنوان بخشی از ساختار میکروکنترلر RISC ارائه شدند. این یک واحد به طور کامل قابل برنامه ریزی می باشد که می تواند با سیگنال های زمان سنج یا داخلی یا خارجی کار کند.

به منظور جلوگیری از توسعه ابزارهای تلفیقی اختصاص داده شده جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

شکل 2. نگاشت حافظه هسته میکروکنترلر RISC

2.1. تشریح جریان دستور العمل

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

شکل 3 . جریان دستور العمل

چرخه واکشی با افزایش ارزش برنامه شمارنده (PC) آغاز می شود. دستورالعمل حافظه برنامه در دستورالعمل (IR) Register در چرخه Q1 تنظیم شده است. سپس این دستورالعمل در طول چرخه های Q2،Q3 و Q4 رمزگشایی و اجرا می شود. حافظه داده در طول Q2 ( عملوند خواندن) خوانده و در طول Q4 (مقصدنوشتن) نوشته می شود.

2.1. خلاصه ای از ویژگی ها

ساختار هسته میکروکنترلر RISC اجرا شده ویژگی های اصلی زیر را ارائه می نماید:

- دستورالعمل هایی با 33 تک کلمه ( 12 بیت عریض)

- سازگاری سطح دستورالعمل با یکی از حالات میکروکنترلر عمومی

- مسیر داده گسترده8 بیتی

- حافظه برنامه خارجی 12 x 512 بیتی

- چندین ثبات خاص + 25 بایت از داده های RAM

- دو سطح عمیق حافظه پشته (Stack) سخت افزار

- حالت های مستقیم، غیر مستقیم و نسبی آدرس دهی برای داده ها و دستورالعمل ها

- زمان سنج بلادرنگ / شمارشگر 8 بیتی (TMR0) با پرسی کالر قابل برنامه ریزی8 بیتی

- نمونه سازی حالت SLEEP

3. روش های طراحی و پیاده سازی

کل میکروکنترلر RISC با استفاده از زبان هندل -C طراحی شده است . هندل -C یک زبان برنامه نویسی خاص می باشد که برای فعال کردن مجموعه ای از برنامه های C مانند در سخت افزار های دیجیتال همزمان طراحی شده است. اگرچه این کار می توانست با استفاده از زبان های تشریح سخت افزار(Hardware Description Languages) سنتی (به عنوان مثال VHDL یا Verilog ) انجام شود، زبان هندل -C را با هدف ارزیابی قابلیت های طراحی سریع و درخور آن برای طراحی هسته دارائی فکری نرم انتخاب نمودیم.

3.1. جریان طراحی هندل- C

جریان طراحی معمول با استفاده از کامپایل سخت افزار مبتنی بر هندل -C در شکل 4 نشان داده شده است. طرح ورودی با استفاده از زبان هندل- C نوشته شده است. هندل-C ساختار زبان جدیدی را ارائه می نماید که اجازه توصیف موازی سخت افزار دیجیتال را می دهد. مجموعه ای غنی از کتابخانه های ماکرو(macro libraries) برای ساده سازی وظایف روتین ارائه شده است.

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

گمارش تکنولوژی هدف خاص و ابزار مسیریابی در کنار نگاشت نت لیست سطح گیتی مورد استفاده قرار گرفته که توسط ابزار هندل-C در دستگاه FPGA هدف ایجاد شده است. در پیاده سازی مان از ابزار Xilinx M2.1i ، همچون FPGA هدف در Xilinx XC4010XL استفاده نمودیم. گمارش FPGA و ابزار مسیریابی موجب ایجاد طرح نهایی طراحی FPGA خواهد شد. ابزار FPGAمی تواند توسط این طرح بندی، همچنین می توانید رشتهی بیت (bitstream) پیکربندی FPGA را ایجاد نماید که در برنامه دستگاه FPGA هدف مورد استفاده قرار خواهد گرفت.

شکل 4 . جریان طراحی کامپایل سخت افزار هندل -C

3.2. پیاده سازی پردازشگر هندل-C

طراحی کامل میکروکنترلر RISC در مدار XESS Corporation XS40 FPGA ،v1.3 ، اجرا شد. در پیاده سازی از مدار اصلی Xilinx XC4010XL FPGA و X 8 بیتی RAM 32 بایتی استفاده شد.

بخش های بعدی، پیاده سازی قسمت های انتخاب شده ساختار هسته میکروکنترلر را به زبان هندل-C توضیح می دهند.

3.2.1. چرخه دستورالعمل

شکل 3 نشان می دهد که هر دستورالعمل مستلزم 4 چرخه Qاست. در طراحی از روتین های اختصاصی هندل-C برای بررسی هر مرحله از دستورالعمل استفاده نمودیم:

Q1 : دستورالعمل واکشی. در طی این مرحله، این دستورالعمل از حافظه برنامه ( حفظ شده در مدار اصلی خارجی RAM در FPGA) خوانده و در دستورالعمل رجیسترIR بارگذاری شده است. مدار اصلی RAM صرفاً 8 بیتی می باشد، در حالی که عرض کلمه دستورالعمل 12 بیت است. بنابراین برای خواندن کل دستورالعمل 12 بیتی به 2 چرخه زمانی نیاز است.

واکشی ماکرو () هندل -C مرحله واکشی چرخه دستورالعمل را اجرا می نماید:

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

به استفاده از ساختار خاص هندل -C در برنامه بالا توجه داشته باشید:

- ایجاد نیروهای برابر موازی با با اجرای عبارات داخل بلاک{} می باشد

- اپراتور@ بیت الحاقی را نشان می دهد

- عملگر word<-N حداقل بیت را از کلمه بر می گرداند

Q2 : عملوند خواندن عملوند منوط به کد دستورالعمل یا توسط حافظه داده ها یا یک تابع رجیستر خاص خوانده خواهد شد. همچنین هسته میکروکنترلر بین حالت های مستقیم و غیر مستقیم آدرس دهی انتخاب می شود. اگر رجیسترINDIR رجیستر منبع(IRL[4:0]==0) باشد، آدرس 5 بیتی ذخیره شده در رجیستر DPTR برای دسترسی غیر مستقیم عملوند ذخیره شده در رجیستر مورد استفاده قرار می گیرد. این عملوند در رجیستر موقت TMP بارگذاری می شود. اگر آدرس عملوند بزرگتر از 6 باشد، فضای حافظه داده در دسترس قرار خواهد گرفت.

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

Q3 : اجرا. در این مرحله رجیستر TMP به عنوان منبع و مقصد عملیات انجام شده توسط دستور العمل استفاده می شود. اگر دستور بر هریک از علامت های پرچم در وضعیت رجیستر تاثیر بگذارد، این امر به صورت موازی با اجرای دستورالعمل ارزیابی می شود. به عنوان مثال، برای ارزیابی کارآمد حالت پرچم Zb در وضعیت رجیستر، عبارت مشترک هندل -C زیر مورد استفاده قرار می گیرد:

shared expr zero(TMP,X)

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

برای دستورالعمل موثر بر جریان کنترل برنامه (به عنوان مثال JUMP،CALL )به یک برنامه نویسی خاص و دو چرخه دستورالعمل نیاز می باشد. عبارت (TMP،X ) addxf مجموع رجیستر X یونیورسال و محتویات رجیستر TMP را ارزیابی می کند.

Q4 : عملوند نوشتن. نتیجه عملیات انجام شده در مرحله Q3 در رجیستر TMP ذخیره شده و برای موقعیت مقصد نوشته شده است. این فرایند مشابه عملوند نوشتن شرح داده شده در Q1 در پاراگراف بالا می باشد.

3.2.2. حافظه

در میکروکنترلر RISC ارائه شده، حافظه در حافظه برنامه و داده ها مجزا گشته است(شکل 2). حافظه پشته نیز به عنوان بخشی از ساختار میکروکنترلر ارائه شده است. در این بخش مولفه های پیاده شازی حافظه را با استفاده از هندل -C بطور خلاصه بیان می کنیم.

حافظه برنامه. حافظه برنامه در این طرح با استفاده از XS40 در مدارRAM که در خارج از FPGA قرار دارد، اجرا شد. هندل- C اجازه تعریف رابط های حافظه خارجی را با استفاده از کلمه کلیدی رم با گزینهoffchip = 1 می دهد:

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

گزینه های دیگر ارائه شده در ساختار رم بالا، ارتباطات واقعی بین پین های FPGA و حافظه داده ها، آدرس و سیگنال های کنترل را تعریف می نماید.

حافظه داده. حافظه داده شامل تعدادی رجیستر با تابع خاص و رجیستر همه منظوره می باشد(شکل 2). این امر در طرح ما، با استفاده از یک فایل رجیستر در داخل FPGA به منظور دسترسی آسان به رجیسترها انجام شد. در مجموع، 25 رجیستر در حافظه داده ها اجرا شد. برای ایجاد حافظه داده ها از عبارت هندل-C استفاده شد:

ram unsigned int DATARAM[25].

حافظه پشته. جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

3.2.3. پورت های I/O

پورت های ورودی / خروجی هسته میکروکنترلر RISC را می توان به راحتی در هندل-C اجرا نمود. همه رابط های خارج از تراشه غیر از RAM ها با کلمه کلیدی رابط شناسایی می شوند. این کلمه کلیدی نوع رابط مورد نیاز و نوع مقادیر مرتبط با اشیاء واردشده توسط رابط را مشخص می کند. تمام پورت ها در اجرای هندل-C ما به شرح زیر تعریف شده است:

interface bus_ts() IOPORTx(GPIO[x], DIRR[x]==0);

که در آن X شاخص پورت است. این نوع رابط کاربری اجازه می دهد تا هندل -C یک ارتباط دو طرفه را از طریق پین های خارجی انجام دهد، که در آن زمانی DIRR [ X ] == 0 می باشد که پین توسط ارزش ذخیره شده در رجیستر GPIO [ X ] تحریک شده باشد.

شکل 5. مقیاس زمانی پروژه

3.3. روش آزمایش

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

به منظور ایجاد طرح بندی طراحی FPGA و رشتهی بیت تنظیمات، نتیجه کامپایل سخت افزار توسطXilinx Alliance M2.1i پردازش شد. در مرحله نهایی، مدار FPGA XS40 با تنظیمات طراحی بارگذاری شد. هنگامی که اولین سخت افزار در حال کار تکمیل شد، طراحی با استفاده از برنامه های کوچک نوشته شده با استفاده از زبان اسمبلی میکروکنترلر RISC مورد آزمایش قرار گرفت. برنامه های متعددی برای این منظور توسعه یافتند، روتین های کنترل ساده برای نمایشLED ، پهنای پالس و یک بازی مبتنی بر ترمینال از این دسته برنامه ها می باشند که به طور کامل ویژگی های میکروکنترلر را اعمال می نمایند.

3.4. مقیاس زمانی پروژه

کل پروژه ، از جمله طراحی برنامه نویسی و شبیه سازی با استفاده از ابزار هندل -C ، توسعه نرم افزار میز آزمون، پیاده سازی FPGA ، اشکال زدایی و ساخت نمونه سخت افزار کمتر از 48 ساعت صورت گرفت. مقیاس زمانی پروژه های واقعی و در طول این پروژه ، در شکل 5 نشان داده شده است.

برنامه نویسی میکروکنترلر RISC ارائه شده حدود 10 ساعت به طول انجامید. این امر شامل برنامه بهینه سازی می باشد که در آن ساختار برنامه بهبود یافته و موانعی برنامه نویسی حذف شده است. پس از اینکه برنامه نویسی به پایان رسید، برنامه ای با زبان ساده اسمبلی که در ابتدا در طول آزمایش شبیه سازی کاربردی HSIM مورد استفاده قرار گرفته بود، برای آزمایش تمام دستورالعمل های میکروکنترلر توسعه یافت.

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

همانطور که در بخش 3.1 نشان داده شده، در مراحل زیر طراحی هندل -C در یک نت لیست سطح گیت گرد هم آمده و بر روی FPGA هدف با استفاده از ابزارهای استاندارد Xilinx نگاشته شده است. طراحی نهایی در سخت افزار زمان واقعی به منظور اصلاح هر گونه مشکل معوق اشکال زدایی شد.

جدول 1 آمار اجرای کلی این پروژه را خلاصه می نماید.

با کامپایلر هندل-C و با استفاده از ابزار HSIM تنها چند ثانیه صرف ایجاد نت لیست مناسب برای شبیه سازی می شود. نت لیست سطح گیت XNF1با کامپایلر هندل-C در PC با ویژگی های محدود تنها ظرف چند دقیقه ایجاد شد.

فرکانس زمانی امکان برای طراحی ما در حدود 30 ٪ بیشتر از دستگاه های میکروکنترلر با تولید انبوه قابل مقایسه است. با این حال، باید خاطر نشان نمودکه دستگاه FPGA مورد استفاده در اجرای ما، بیشتر از میکروکنترلرها مبتنی بر فن آوری های پیشرفته می باشد.

4. نتیجه گیری

مطالعه موردی طراحی هسته میکروکنترلرRISC را با استفاده از هندل -C جریان طراحی کامپایل سخت افزار نشان دادیم. در حالی که برنامه نویسی طراحی میکروکنترلر تنها 12 ساعت زمان برد، تکمیل و آزمایش کل طرح در سخت افزار FPGA واقعی کمتر از 48 ساعت انجام شد.

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

Design of a RISC Microcontroller Core in 48 Hours

طراحی هسته میکروکنترلر کامپیوتر مجموعه دستورالعمل هاى کاسته شده در 48 ساعت

ISI

Paper

Papers

Article

کامپیوتر

Articles

مقاله ISI

دانلود ISI

طراحی هسته

ترجمه مقاله

میکروکنترلر

ISI کامپیوتر

دریافت مقاله

Persian Paper

مقاله انگلیسی

خرید ترجمه ISI

ترجمه مقاله ISI

Persian Article

مقاله رایگان ISI

خرید ترجمه مقاله

دانلود مقاله ISI

دانلود ترجمه ISI

مقالات رایگان ISI

دریافت مقالات ISI

دانلود مقاله جدید

مجموعه دستورالعمل

فروش ترجمه انگلیسی

خرید ترجمه انگلیسی

مقاله انگلیسی جدید

مقاله ISI با ترجمه

مقاله ISI کامپیوتر

ترجمه مقاله انگلیسی

دانلود ISI کامپیوتر

دانلود مقاله انگیسی

ترجمه مقاله کامپیوتر

مقالات معتبر انگلیسی

ترجمه مقالات انگلیسی

دریافت مقاله انگلیسی

دانلود مقاله جدید ISI

دریافت مقاله کامپیوتر

مقاله انگلیسی کامپیوتر

مقاله انگلیسی با ترجمه

Translate English Paper

دانلود رایگان مقاله ISI

خرید ترجمه ISI کامپیوتر

دانلود مقالات رایگان ISI

ترجمه مقاله ISI کامپیوتر

دانلود مقاله ISI با ترجمه

Translate English Article

دانلود مقاله انگلیسی جدید

خرید ترجمه مقاله کامپیوتر

دانلود ترجمه ISI کامپیوتر

دانلود مقاله ISI کامپیوتر

مقاله رایگان ISI کامپیوتر

دریافت مقاله انگلیسی جدید

Translate Paper in English

دانلود مقاله جدید کامپیوتر

دریافت مقالات ISI کامپیوتر

ترجمه مقالات معتبر انگلیسی

مقالات رایگان ISI کامپیوتر

دانلود مقاله انگلیسی رایگان

دانلود رایگان مقاله انگلیسی

دانلود مقاله انگلیسی رایگان

دریافت مقاله انگلیسی رایگان

مقاله انگلیسی جدید کامپیوتر

خرید ترجمه انگلیسی کامپیوتر

مقاله ISI با ترجمه کامپیوتر

فروش ترجمه انگلیسی کامپیوتر

Translate Article in English

ترجمه مقاله انگلیسی کامپیوتر

دانلود مقاله انگیسی کامپیوتر

دریافت مقاله انگلیسی با ترجمه

دانلود مقاله انگلیسی با ترجمه

دریافت مقاله انگلیسی کامپیوتر

ترجمه مقالات انگلیسی کامپیوتر

مقالات معتبر انگلیسی کامپیوتر

دانلود مقاله جدید ISI کامپیوتر

Translation of Paper in English

مقاله انگلیسی با ترجمه کامپیوتر

دانلود رایگان مقاله ISI کامپیوتر

Translation of Article in English

دانلود مقالات رایگان ISI کامپیوتر

دریافت مقاله انگلیسی جدید کامپیوتر

دانلود مقاله انگلیسی جدید کامپیوتر

دانلود مقاله ISI با ترجمه کامپیوتر

ترجمه مقالات معتبر انگلیسی کامپیوتر

دریافت مقاله انگلیسی رایگان کامپیوتر

دانلود مقاله انگلیسی رایگان کامپیوتر

دانلود مقاله انگلیسی رایگان کامپیوتر

دانلود رایگان مقاله انگلیسی کامپیوتر

دانلود مقاله انگلیسی با ترجمه کامپیوتر

دریافت مقاله انگلیسی با ترجمه کامپیوتر

به سوی پایگاه داده چندگانه (اشتراکی) انعطاف پذیر و مستقل

.png)

.png)

Abstract The success of cloud computing as a platform for deploying webapplications has led to a deluge of applications characterized by small data footprints with unpredictable access patterns. A scalable multitenant ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

رویکردی در ارتباط با معماری خط تولید سرویسگرا

.png)

.png)

Abstract Service-Oriented Architecture (SOA) has appeared as an emergent approach for developing distributed applications as a set of self-contained and business-aligned services. SOA aids solving integration and interoperability problems and provides ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

ظرفیت شبکه های بی سیم

.png)

.png)

Abstract When n identical randomly located nodes, each capable of transmitting at W bits per second and using a fixed range, form a wireless network, the throughput (formula) obtainable by each ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 139500 تومان

قیمت: 139500 تومان

قیمت: 139500 تومان

قیمت: 139500 تومان

سیستم های صف بندی زمان گسسته با تعطیلی های انحصاری مارکوفب

.png)

.png)

Abstract In this contribution we investigate discrete-time queueing systems with vacations. A framework is constructed that allows for studying numerous different vacation systems, including a.o. classical vacation systems like the exhaustive ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

عوامل تعیینکننده در انتخاب نرمافزار وبمحور معنایی در قالب یک سرویس:

چارچوبی یکپارچه در شرایط خرید الکترونیکی و برنامه ریزی منابع سرمایه ای

.png)

.png)

Abstract The ever increasing Internet bandwidth and the fast changing needs of businesses for effectiveness with the partners in the procurement chain and is leading organizations to adopt information systems infrastructures ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

طراحی و تحلیل یک مدل وقفه (تعطیلی) برای سیستم صف بندی دو فازه با خدمات ورودی

.png)

.png)

Abstract This paper mainly deals with a two phase service queueing model with gated service vacation. In this gated service vacation model, only those customers who are present in the queue ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

به اشتراک گذاری طیف مشارکتی بین شبکه های تلفن همراه و اد هاک

.png)

.png)

Abstract Spectrum sharing between cellular and ad-hoc networks is studied in this work. Weak signals and strong interferences at the cell-edge area usually cause severe performance degradation. To improve the cell-edge ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 139500 تومان

قیمت: 139500 تومان

قیمت: 139500 تومان

قیمت: 139500 تومان

مقایسه پروتکل های مسیر یابی تک مسیره در مقابل پروتکل های مسیر یابی چندگانه برای انتقال تصویر در شبکه های حسگر بی سیم چند رسانه ای

.png)

.png)

Abstract Wireless multimedia sensor network (WMSN) applications require strong multimedia communication competence. Therefore, in WMSN applications, it is necessary to use specific mechanisms in order to handle multimedia communication challenges and ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

هوش کسب و کار به روش محاسبه ابری

.png)

.png)

Abstract Business Intelligence (BI) deals with integrated approaches to management support. Currently, there are constraints to BI adoption and a new era of analytic data management for business intelligence these constraints ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

مدل احتمال جدید برای ضمانت کردن مشکل مسیر بحرانی با الگوریتم اکتشافی

.png)

.png)

Abstract In order to obtain an adequate description of risk aversion for insuring critical path problem, this paper develops a new class of two-stage minimum risk problems. The first-stage objective function ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

دستورالعمل طراحی و محاسبه سیستم روشنایی

.png)

.png)

مجموعه دستورالعمل های ارائه شده در دیتاسرا شامل ضوابط و مراحل تحلیل و طراحی سازه های گوناگون صنعتی و بر اساس الزامات مندرج در آیین نامه های معتبر داخلی و ... [ ادامه مطلب ]

قیمت: 119500 تومان

مشخصات کلی:

قیمت: 119500 تومان

مشخصات کلی:

صفحات متن اصلی: 30

گروه:

دستورالعمل طراحی

قیمت: 119500 تومان

قیمت: 119500 تومان

صفحات متن اصلی: 30

گروه: دستورالعمل طراحی

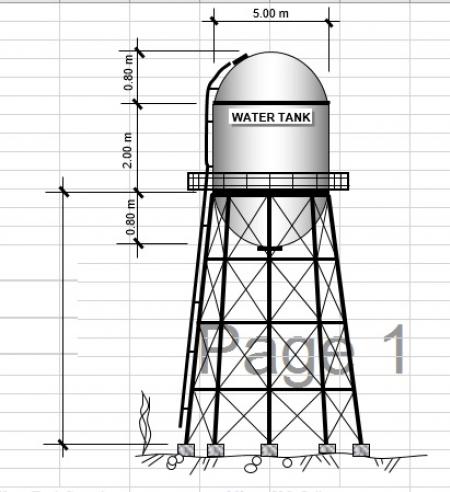

فایل اکسل طراحی مخزن فلزی هوایی بر اساس آیین نامه AISC با در نظر گرفتن نیروی باد و زلرله

.png)

.png)

فایل پیش رو اکسل طراحی مخزن فلزی هوایی می باشد که بر اساس آیین نامه AISC و با در نظر گرفتن نیروی باد و زلرله محاسبات را انجام داده و ... [ ادامه مطلب ]

قیمت: 79500 تومان

مشخصات کلی:

قیمت: 79500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 79500 تومان

قیمت: 79500 تومان

گروه: دستورالعمل طراحی

فایل اکسل تحلیل اتصال برشی دارای خروج از مرکزیت برای گروه پیچ

.png)

.png)

این برنامه ظرفیت برشی اتصال پیچ و مهره ای دارای خروج از مرکزیت برای گروه پیچ را محاسبه می کند، ابزاری مناسب برای طراحی صفحات gusset و اتصالات پیچ و ... [ ادامه مطلب ]

قیمت: 79500 تومان

مشخصات کلی:

قیمت: 79500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 79500 تومان

قیمت: 79500 تومان

گروه: دستورالعمل طراحی

فایل اکسل طراحی روسازی آسفالتی بر مبنای آیین نامه آشتو و استفاده از آزمایش ظرفیت باربری کالیفرنیا

.png)

.png)

فایل پیش رو اکسل طراحی روسازی آسفالتی بر مبنای آیین نامه آشتو می باشد که با استفاده از نتایج آزمایش ظرفیت باربری کالیفرنیا CBR اطلاعات ورودی را تحلیل و نتایج را ... [ ادامه مطلب ]

قیمت: 79500 تومان

مشخصات کلی:

قیمت: 79500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 79500 تومان

قیمت: 79500 تومان

گروه: دستورالعمل طراحی

دستورالعمل طراحی ابعاد و سازه شالوده های عمیق (شمع ها و پایه های عمیق) در خشکی

.png)

.png)

مجموعه دستورالعمل های ارائه شده در دیتاسرا شامل ضوابط و مراحل تحلیل و طراحی سازه های گوناگون صنعتی و بر اساس الزامات مندرج در آیین نامه های معتبر داخلی و ... [ ادامه مطلب ]

قیمت: 119500 تومان

مشخصات کلی:

قیمت: 119500 تومان

مشخصات کلی:

صفحات متن اصلی: 27

گروه:

دستورالعمل طراحی

قیمت: 119500 تومان

قیمت: 119500 تومان

صفحات متن اصلی: 27

گروه: دستورالعمل طراحی

تحلیل غیرخطی و مدل سازی عددی تیر بتن مسلح تقویت شده با FRP توسط Finite Element Method

.png)

.png)

"پایان نامه مهندسی عمران مقطع کارشناسی ارشد - گرایش سازه" تحلیل غیرخطی و مدل سازی عددی تیر بتن مسلح تقویت شده با FRP توسط Finite Element Method مشخصات کلی: شامل فایلهای word و ... [ ادامه مطلب ]

قیمت: 129500 تومان

مشخصات کلی:

قیمت: 129500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 129500 تومان

قیمت: 129500 تومان

گروه: دستورالعمل طراحی

بررسی پارامترهای هندسی مهاربند زانویی

.png)

.png)

"پروژه دانشجویی مهندسی عمران" بررسی پارامترهای هندسی مهاربند زانویی مشخصات کلی: شامل فایلهای word و pdf بالغ بر 146 صفحه (4 فصل) فهرست مطالب فصل اول 1-1- مقدمه 1-2- شکل پذیری سازه ها 1-3- مفصل و لنگر پلاستیک 1-4- منحنی ... [ ادامه مطلب ]

قیمت: 129500 تومان

مشخصات کلی:

قیمت: 129500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 129500 تومان

قیمت: 129500 تومان

گروه: دستورالعمل طراحی

تحلیل و طراحی سیستم گرمایشی ساختمان مسکونی با استفاده از ذخیره کننده های حرارتی PCM

.png)

.png)

"پایان نامه مهندسی مکانیک مقطع کارشناسی ارشد - گرایش تبدیل انرژی" تحلیل و طراحی سیستم گرمایشی ساختمان مسکونی با استفاده از ذخیره کننده های حرارتی PCM تهیه شده بصورت کاملا انحصاری توسط ... [ ادامه مطلب ]

قیمت: 449000 تومان

مشخصات کلی:

قیمت: 449000 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 449000 تومان

قیمت: 449000 تومان

گروه: دستورالعمل طراحی

شناسایی و رتبه بندی دلایل انحراف از هزینه پیش بینی شده و ارائه راهکارهای کاهش آن: مطالعه موردی پروژه های "پتروشیمی الف"

.png)

.png)

"پایان نامه مهندسی عمران مقطع کارشناسی ارشد - گرایش مهندسی و مدیریت ساخت" شناسایی و رتبه بندی دلایل انحراف از هزینه پیش بینی شده و ارائه راهکارهای کاهش آن: مطالعه ... [ ادامه مطلب ]

قیمت: 259500 تومان

مشخصات کلی:

قیمت: 259500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 259500 تومان

قیمت: 259500 تومان

گروه: دستورالعمل طراحی

مکانیک شکست (Fracture Mechanics)

.png)

.png)

مقدمه : یکی از عمده ترین مسائلی که انسان از زمان ساختن سادهترین ابزارها با آن مواجه بوده است پدیده شکست در اجسام میباشد و درواقع برای استفاده از مواد ... [ ادامه مطلب ]

قیمت: 99500 تومان

مشخصات کلی:

قیمت: 99500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 99500 تومان

قیمت: 99500 تومان

گروه: دستورالعمل طراحی

.png)