ریزپردازنده ای قابل حمل و با قابلیت تحمل خرابی مبتنی بر ساختار اسپارک وی 8 A Portable and Fault-Tolerant Microprocessor Based on the SPARC V8 Architecture

Abstract

The architecture and implementation of the LEON-FT processor is presented. LEON-FT is a fault-tolerant 32-bit processor based on the SPARC V8 instruction set. The processors tolerates transient SEU errors by using techniques such as TMR registers, on-chip EDAC, parity, pipeline restart, and forced cache miss. The first prototypes were manufactured on the Atmel ATC35 0.35 μm CMOS process, and subjected to heavy-ion fault-injection at the Louvain Cyclotron. The heavy-ion tests showed that all of the injected errors (> 100,000) were successfully corrected without timing or software impact. The device SEU threshold was measured to be below 6 MeV while ion energy-levels of up to 110 MeV were used for error injection.

چکیده فارسی

در اینجا ساختار و پیاده سازی پردازنده LEON-FT ارائه شده است. LEON-FT پردازنده ای 32 بیتی با قابلیت تحمل خرابی می باشد که مبتنی بر مجموعه ای از دستورالعمل های SPARC V8 است. پردازنده ها با استفاده از روش هایی مانند رجیستر TMR، EDAC روی تراشه، بیت توازن، راه اندازی مجدد خط لوله و نبود اجباری حافظه نهان خطای گذرای خرابیSEU را تحمل می نمایند. اولین نمونه های اولیه توسط Atmel ATC35 0.35 µm CMOS ساخته شد و تزریق خطای یون سنگین در لووین سیکلوترون تحت کنترل در آمد. آزمون های یون سنگین نشان داد که تمام خطاهای تزریق شده(100000<) با موفقیت و بدون تاثیر زمان بندی یا نرم افزاری اصلاح شدند. سطح تنظیم دستگاه SEU در حالی زیر 6 MeV اندازه گیری شد که سطح انرژی یون برای تزریق خطا تا 110 MeV مورد استفاده قرار گرفت.

مشخصات

توسط: Jiri Gaisler مجله: International Conference on Dependable Systems and Networks انتشارات: IEEE سال انتشار: 2002 میلادی تعداد صفحات متن اصلی: 7 تعداد صفحات متن ترجمه: 19 تاریخ درج: ۱۳۹۵/۷/۳ منبع: دیتاسرا

خرید آنلاین فایل ترجمه

عنوان: ریزپردازنده ای قابل حمل و با قابلیت تحمل خرابی مبتنی بر ساختار اسپارک وی 8 حجم: 416.68 کیلوبایت فرمت فایل: pdf قیمت: 119500 تومان رمز فایل (در صورت نیاز): www.datasara.com نرم افزارهای مورد نیاز: winrar - adobe acrobat - office

تنها با ارسال یک ایمیل وجه خود را دریافت نمایید

دانلود فایل اصلی

عنوان: A Portable and Fault-Tolerant Microprocessor Based on the SPARC V8 Architecture

مقدمه

در سال 1997، آژانس فضایی اروپا (ESA) توسعه ریزپردازنده 32 بیتی را برای برنامه های کاربردی فضای پرواز تعبیه شده که با ERC32 نشان داده شده، تکمیل نمود. ERC32 ، مبتنی بر پردازنده Cypress CY601 SPARC V7 می باشد و در حال حاضر در چندین پروژه فضایی، از جمله کامپیوتر های کنترل ایستگاه فضایی بین المللی مورد استفاده قرار گرفته است. در سال 1998 برای مطابقت با الزامات ماموریت پروژه های ماورای سال 2000، توسعه پردازنده جدید و بهبود یافته ای تحت عنوانLEON آغاز شد. این مقاله اهداف طراحی، ساختار، توابع با قابلیت تحمل خرابی توکار و نتایج تست اولیه این پردازنده. را ارائه می نماید پروژه LEON توسط ESA تحت مشارکت داگلاس مارش و برنامه ریزی تحقیقاتی فناوری ESA (TRP) آغاز شد و در حال حاضر توسط تحقیقات گیسلر تحت قرارداد ESTEC به شمارهFM /NL /01/15102 ادامه دارد.

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

2. پیش زمینه

ریزپردازنده اروپایی طراحی شده برای برنامه های کاربردی فضایی، به طور معمول دارای سه طراحی درایور های اصلی می باشند: تابش- سختی، عملکرد و هزینه توسعه. اهداف با بودجه محدودی انجام شده اند، دستگاهی را ایجاد می نماید که می تواند محیط تابش فضا را مقاوم سازد و بالاترین کارایی ممکن را با فرآیند نیمه هادی مشخص ارائه دهد. افزایش پیچیدگی و حجم ماهواره های جدید الزاماتی را برای کاهش هزینه، یکپارچه سازی بیشتر، استفاده از نرم افزارهای تجاری با تولید انبوه و عملکرد بالاتر ارائه می نماید. افزایش سرعت توسعه تکنولوژی میکرو الکترونیک پیچیدگی های بیشتری ارائه می نماید؛ عمر فرآیندهای نیمه هادی در حال کاهش به سوی نقطه ای می باشدکه در آن تضمین مولفه پشتیبان با طول عمر بالا دشوار و مستلزم برنامه های فضایی زیادی می باشد. علاوه بر این، تقاضا برای مولفه های نظامی از زمان پایان جنگ سرد، کاهش تعداد ریخته گری ارائه دهنده مولفه های تابش-سخت و ایجاد خدمات، به طور قابل توجهی کاهش یافته است.

هدف پردازنده LEON مطابقت با الزامات مورد نیاز برای عملکرد، دسترس پذیری و هزینه پایین با استفاده از استانداردهای تجاری، روش طراحی و تکنولوژی نیمه هادی می باشد. اهداف طراحی زیر برای پردازنده تعریف شده اند:

- استفاده از فرایند نیمه هادی های تجاری. پیاده سازی پردازنده در فرآیندهای تجاری و واژگونی تک رویداد (SEU) نیمه هادی حساس برای کاهش هزینه و افزایش کارایی امکان پذیر می باشد.

- قابلیت حمل. پردازنده باید برای تضمین دسترس پذیری بلند مدت، ، در حین حفظ عاملیت و کارائی، در طیف گسترده ای از فرآیندهای نیمه هادی با حداقل هزینه و تلاش قابل حمل باشد.

- پیمانه ای بودن. پیاده سازی پردازنده باید اجازه استفاده مجدد در طرح های سیستم روی تراشه (SOC) را بدهد.

- مقیاس پذیری. پردازنده باید با حداقل سخت افزار و نرم افزار های سربار هم در برنامه های کاربردی رده پایین و هم برنامه های رده بالا قابل استفاده باشد.

- رابط های استاندارد. پردازنده باید رابط ها را برای ساده نمودن یکپارچه سازی سیستم ها و استفاده مجدد از هسته ها، مولفه ها و ابزار تجاری استاندارد نماید.

- سازگاری با نرم افزار. پردازنده باید با ابزار توسعه نرم افزاری ERC32 و COTS بسته های نرم افزاری در حال حاضر مورد استفاده سازگار باشد.

سطح کارائی موردنظر 100 MIPS (اوج) در 100 MHz ، با مصرف برقی کمتر از 1 وات می باشد.

3. ساختار LEON

پردازنده LEON بر اساس واحد عدد صحیح سازگار با SPARCV8 می باشد که به تازگی توسعه یافته است، این برنامه شامل یک خط لوله 5 مرحله ای، ضرب سخت افزاری و واحد های تقسیم، رابط های پردازنده کمکی دوگانه و دستورالعمل مجزا و باس های اطلاعاتی (ساختار هاروارد) می باشد. دلیل انتخاب ساختار SPARCV8 دو چندان می باشد: برای حفظ سازگاری نرم افزار با ERC32 و برای جلوگیری از هر گونه مسائل صدور مجوز در مورد پیاده سازی مجدد مجموعه ای از دستورالمل ها (SPARC یک ساختار باز می باشد و می تواند بدون مجوز استفاده شود). باس سرعت بالای AMBA AHB برای انتقال داده بین حافظه های نهان و کنترلر حافظه ی خارجی استفاده می شود. باس سرعت پایینAMBA APB برای اتصال دستگاه های جانبی ساده تر متصل بر روی تراشه مانند زمان سنج ها، uartها، کنترل کننده وقفه و پورت های I/O مورد استفاده قرار می گیرد. نمودار کلی را می توان در شکل 1 در زیر مشاهده نمود:

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

شکل 1: نمودار کلی LEON

4. انطباق با محیط زیست فضایی

4.1. اهداف طرح

یکی از اهداف اصلی طرح برایLEON، توانایی استفاده از واژگونی تک رویداد(SEU) فرآیند نیمه هادی حساس، در حین حفظ عملکرد صحیح در محیط فضا می باشد. آزمون های گسترده در ERC32 نشان داد که تشخیص خطا برای حفظ عملکرد صحیح، بدون استفاده از کامپیوتر یا رای گیری کافی نیست. برای جلوگیری از سربار زیادی در واحد های یدکی، تصمیم گرفته شد که تحمل خرابی بر روی تراشه برای شناسایی و حذف خطاهای SEU اجرا شود. حذف خطا برای توانایی استفاده از نرم افزار COTS اصلاح نشده، باید به طور نرم افزاری کاملاً شفاف و بدون تاثیر (یا با قابل جزئی) در کارایی باشد. برای حفظ قابلیت حمل، توابع تحمل خرابی باید به طور مستقیم در VHDL بدون تکیه بر سلول های فن آوری سخت SEU اجرا شوند.

4.2. تجزیه و تحلیل اولیه

برای اولین طرحLEON، تنها خطاهای SEU نشات گرفته از ضربه مستقیم به عامل رجیستر یا حافظه در نظر گرفته شد. آزمایشات نشان داده است که خطاهای SEU در منطق ترکیبی می تواند در رجیستر باس ساعت انتشار یابد، اما احتمال چنین رویدادی کم است.

مطالعه در مورد توزیع سلول های ترتیبی در طراحی LEON، سه گروه را ایجاد می نماید: سلول های تک پورت حافظه با دسترسی تصادفی برای حافظه های نهان (برچسب ها و داده ها)، حافظه با دسترسی تصادفی سه پورت مورد استفاده برای فایل رجیستر پردازنده و فلیپ فلاپ های- D همزمان مورد استفاده برای تمام حافظه های ذخیره سازی از قبیل ماشین های حالت، رجیسترهای خط لوله و توابع وضعیت/کنترل. برای این سه گروه بر اساس کاربرد شان در سیستم از انواع مختلف عمل حفاظت SEU استفاده شده است.

4.3. حافظه های پنهانی

حافظه های نهان بزرگ برای کارایی های بالا حیاتی می باشند و به طور معمول در مسیر بحرانی پردازنده (زمان بندی) قرار دارند. این امر در واقع برای LEON درست می باشد که به دلیل قابلیت حمل به جای استفاده از سلول های ram استاندارد و همزمان از ramهایی استفاده می شود که به طور خاص طراحی شده اند. ramهای حافظه نهان با تشخیص خطای ساده در قالب یک یا دو بیت توازن برای هر برچسب یا کلمه داده، برای به حداقل رساندن پیچیدگی و سربار زمانی ارائه شده اند. بیت های توازن به طور همزمان با برچسب یا داده های مربوط نوشته شده اند و در هر دسترسی بررسی شده اند. اگر خطای توازن در طول دسترسی حافظه نهان حافظه تشخیص داده شود، فقدان حافظه نهان (cache miss ) اجباری می باشد و اطلاعات (خراب) از حافظه خارجی واکشی می شود. حافظه نهان از سیاست یکسره نویسی(write-through) استفاده می نماید و بنابراین نسخه دوم از داده ها همیشه در دسترس است. تا زمانی که بررسی توالی در موازات بررسی برچسب انجام نشود، جریمه زمانی رخ نمی دهد.

در بلوک های متراکم ram، یک ضربه SEU می تواند منجر به خطاهای متعدد در سلول های مجاور گردد. اگر بیت ها در بلوکram بطور هندسی به عنوان ماتریسی با یک کلمه در هر خط سازمان یافته باشد، خطای متعدد می تواند در همان کلمه رخ دهد که به طور بالقوه توسط یک بیت توازن تشخیص داده نمی شود (بیت توازن واحد صرفاً می تواند خطاهایی با عدد فرد را تشخیص دهد) . برای رسیدگی به مواردی چون سلول هایram، می توان LEON را برای استفاده از دو بیت توازن در برچسب ها و داده های کلمه، یکی برای بیت داده با اعداد فرد و دیگری برای بیت داده با اعداد زوج تنظیم نمود. سپس می توان خطای مضاعف در هر سلول مجاور را تشخیص داد. در ramهایی با کلمات داده ای بطور هندسی جاگذاری شده (یعنی، هیچ بیت مجاوری متعلق به همان کلمه نیست)، تشخیص یک بیت توازن با خطاهای مضاعف کافی است.

4.4. پردازشگر فایل رجیستر

ساختار SPARC از رجیسترهای ویندوز 32 بیتی استفاده می نماید(16 همپوشانی). اجرای ویندوز 8 شامل 136 رجیستر عدد صحیح 32 بیتی و 32 رجیستر ممیز شناور 32 بیتی می باشد. اکثر دستورالعمل های SPARC از دو منبع و یک عملوند مقصد استفاده می نمایند، در نتیجه پردازنده LEON از سه پورت فایل رجیستر استفاده می کند. برای تشخیص خطاهای SEU، هر کلمه را می توان با استفاده از یک بیت توازن، دو بیت توازن یا یک BCH (32،7) مقابله ای حفظ نمود. بیت های محفاظت در مرحله نوشتن خط لوله ایجاد شده و همراه با داده های مربوطه نوشته شده اند. فایل رجیستر در مرحله رمزگشایی خوانده می شود، اما برای اجتناب از جریمه های زمانی در مرحله رمزگشایی، بررسی آن در مرحله اجرایی به صورت موازی با اجرای دستورالعمل ها انجام می شود. اگر یک خطای قابل اصلاح تشخیص داده شود (شکل 2ج)، خط لوله بخشی از حافظه و محتویات آن را خالی می کند و عملوند نادرست داده اصلاح شده و دوباره در فایل رجیستر نوشته می شود (به جای نتایج دستورالعمل نادرست). سپس خط لوله در نقطه دستورالعمل شکست بطور مجدد راه اندازی شد. عملیات راه اندازی مجدد دقیقاً مشابه به دام انداختن می باشد با این استثنا که در آدرس دهی دستور العمل شکست خورده به جای بردار تله، یک پرش ایجاد می شود. عملیات راه اندازی مجدد کامل 4 سیکل زمانی به طول می انجامد و به دام اندازی نرمال هم همین مقدار زمان می برد. اگر خطای غیر قابل اصلاحی تشخیص داده شود (شکل 2 د)، تله خطای رجیستر ایجاد می شود. سربار پیاده سازی برای راه اندازی مجدد خط لوله کوچک است زیرا برای رسیدگی به تله نرمال از منطق استفاده می شود. شکل 2ب رفتار خط لوله ای یک تله طبیعی را نشان می دهد.

فایل رجیستر دارای دو پورت خواندن می باشد و با دو واحد تشخیص خطا اجرا می شوند. فایل رجیستر دارای یک پورت نوشتن، و تنها یک واحد تصحیح می باشد. این بدان معنی است که اگر بیش از یک خطای قابل اصلاح رخ دهد، این دستورالعمل در هر زمان برای هر خطا و اصلاح و ذخیره مقدار رجیستر صرفاً یک بار راه اندازی مجدد خواهد شد. در بدترین حالت، دستور العمل ذخیره سازی دوبلی که از چهار رجیستر واحد استفاده می نماید را می توان تا چهار بار راه اندازی مجدد نمود و بدین طریق می توان در یک زمان یک مقدار رجیستر را اصلاح نمود.

استانداردترین سلول مجموعه برنامه هایram دربردارنده ram سه پورت نیست و سپس فایل رجیستر به عنوان دو ram دو پورت در موازات پورت های نوشتن متصل به هم اجرا شده است. در چنین موردی، نه تنها برای تشخیص خطا بلکه برای اصلاح آنها می توان از کدهای توازن ارزان تری استفاده نمود. ram های دو پورت دارای محتوای یکسان می باشند و هنگامی که یک خطای توازن بر روی پورت خوانش شناسایی شد (یعنی در یک حافظه)، تصحیح خطا با کپی مقدار حافظه بدون خطا برای حافظه شکست خورده انجام می شود. در طول عملیات کپی، ram بدون خطا (مفروض) نیز برای خطاها بررسی می شود، اگر خطایی یافت شود، تله خطای غیر قابل تصحیح ایجاد می شود.

اگر چه طرح حفاظت اجراشده (توازن یاBCH) هیچگونه تاثیر زمانی نداشته باشد، سطح کارائی دستورالعمل های ذخیره سازی دوگانه را می توان کمی تحت تاثیر قرار داد. به همین دلیل است که بافر نوشتن در حافظه نهان داده درخواست باس حافظه را در یک چرخه زمانی به تاخیر خواهد انداخت تا هیچ چرخه ذخیره حافظه ای قبل از بررسی و اصلاح(بالقوه) ذخیره ثانوی کلمه داده آغاز نگردد.

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

شکل 2: عملیات خط لوله در تله ها و خطاها

فلیپ فلاپ ها

پردازنده شامل حدود 2500 فلیپ فلاپ، مورد استفاده برای ذخیره سازی موقت و حالت ماشینی می باشد. برای محافظت در برابر خطاهای SEU، هر رجیستر بر روی تراشه را می توان با استفاده از افزونگی مدولار سه گانه (TMR) اجرا نمود. فلیپ فلاپ ها به طور مداوم زمان سنجی شده و هر گونه خطای رجیستر SEU به طور خودکار در یک چرخه زمانی حذف خواهد شد، در حالی که خروجی رای دهنده مقدار صحیح (بدون گلیچ) را حفظ خواهد نمود. برای افزایش بیشتر استحکام ، هر یک از سه مسیر رجیستر TMR دارای درخت های زمانی جداگانه می باشد (شکل 3). بنابراین یک ضربه SEU در یک درخت زمانی حتی اگر داده ها از مسیر کامل از 2500 رجیستر تغییر یابد، می تواند تحمل شود. در باس ساعت ذیل، تمام خطاها زمانی حذف خواهد شد که اطلاعات جدید زمان سنجی شده باشد. ضربهSEU در پد زمانی(واحد) به این دلیل تحمل نمی شود که در هر سه درخت زمانی را انتشار خواهد یافت. با این حال، میزان بالای ویژگی ها و ظرفیت بافر زمانی اصلی، موجب چنین رویداد بعیدی می شود.

جهت مشاهده متن کامل، فایل ترجمه را دانلود نمایید.

A Portable and FaultTolerant Microprocessor Based on the SPARC V8 Architecture

ریزپردازنده ای قابل حمل و با قابلیت تحمل خرابی مبتنی بر ساختار اسپارک وی 8

ISI

Paper

Papers

Article

قابل حمل

Articles

مقاله ISI

تحمل خرابی

دانلود ISI

ریزپردازنده

ترجمه مقاله

ISI کامپیوتر

دریافت مقاله

Persian Paper

مقاله انگلیسی

خرید ترجمه ISI

Persian Article

ترجمه مقاله ISI

مقاله رایگان ISI

دانلود مقاله ISI

خرید ترجمه مقاله

دانلود ترجمه ISI

دریافت مقالات ISI

دانلود مقاله جدید

مقالات رایگان ISI

مقاله ISI با ترجمه

ساختار اسپارک وی 8

مقاله ISI کامپیوتر

خرید ترجمه انگلیسی

مقاله انگلیسی جدید

فروش ترجمه انگلیسی

دانلود ISI کامپیوتر

ترجمه مقاله انگلیسی

دانلود مقاله انگیسی

مقالات معتبر انگلیسی

ترجمه مقالات انگلیسی

ترجمه مقاله کامپیوتر

دریافت مقاله انگلیسی

دانلود مقاله جدید ISI

دریافت مقاله کامپیوتر

مقاله انگلیسی کامپیوتر

مقاله انگلیسی با ترجمه

دانلود رایگان مقاله ISI

خرید ترجمه ISI کامپیوتر

Translate English Paper

ترجمه مقاله ISI کامپیوتر

دانلود مقالات رایگان ISI

دانلود مقاله ISI با ترجمه

Translate English Article

دانلود ترجمه ISI کامپیوتر

خرید ترجمه مقاله کامپیوتر

مقاله رایگان ISI کامپیوتر

دانلود مقاله انگلیسی جدید

دریافت مقاله انگلیسی جدید

دانلود مقاله ISI کامپیوتر

ترجمه مقالات معتبر انگلیسی

Translate Paper in English

دریافت مقالات ISI کامپیوتر

مقالات رایگان ISI کامپیوتر

دانلود مقاله جدید کامپیوتر

مقاله ISI با ترجمه کامپیوتر

دانلود مقاله انگلیسی رایگان

دریافت مقاله انگلیسی رایگان

دانلود مقاله انگلیسی رایگان

خرید ترجمه انگلیسی کامپیوتر

دانلود رایگان مقاله انگلیسی

مقاله انگلیسی جدید کامپیوتر

فروش ترجمه انگلیسی کامپیوتر

Translate Article in English

ترجمه مقاله انگلیسی کامپیوتر

دانلود مقاله انگیسی کامپیوتر

مقالات معتبر انگلیسی کامپیوتر

ترجمه مقالات انگلیسی کامپیوتر

دریافت مقاله انگلیسی با ترجمه

دریافت مقاله انگلیسی کامپیوتر

دانلود مقاله انگلیسی با ترجمه

دانلود مقاله جدید ISI کامپیوتر

مقاله انگلیسی با ترجمه کامپیوتر

Translation of Paper in English

دانلود رایگان مقاله ISI کامپیوتر

دانلود مقالات رایگان ISI کامپیوتر

Translation of Article in English

دانلود مقاله ISI با ترجمه کامپیوتر

دریافت مقاله انگلیسی جدید کامپیوتر

دانلود مقاله انگلیسی جدید کامپیوتر

ترجمه مقالات معتبر انگلیسی کامپیوتر

دانلود مقاله انگلیسی رایگان کامپیوتر

دانلود رایگان مقاله انگلیسی کامپیوتر

دریافت مقاله انگلیسی رایگان کامپیوتر

دانلود مقاله انگلیسی رایگان کامپیوتر

دریافت مقاله انگلیسی با ترجمه کامپیوتر

دانلود مقاله انگلیسی با ترجمه کامپیوتر

به سوی پایگاه داده چندگانه (اشتراکی) انعطاف پذیر و مستقل

.png)

.png)

Abstract The success of cloud computing as a platform for deploying webapplications has led to a deluge of applications characterized by small data footprints with unpredictable access patterns. A scalable multitenant ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

رویکردی در ارتباط با معماری خط تولید سرویسگرا

.png)

.png)

Abstract Service-Oriented Architecture (SOA) has appeared as an emergent approach for developing distributed applications as a set of self-contained and business-aligned services. SOA aids solving integration and interoperability problems and provides ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

ظرفیت شبکه های بی سیم

.png)

.png)

Abstract When n identical randomly located nodes, each capable of transmitting at W bits per second and using a fixed range, form a wireless network, the throughput (formula) obtainable by each ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 139500 تومان

قیمت: 139500 تومان

قیمت: 139500 تومان

قیمت: 139500 تومان

سیستم های صف بندی زمان گسسته با تعطیلی های انحصاری مارکوفب

.png)

.png)

Abstract In this contribution we investigate discrete-time queueing systems with vacations. A framework is constructed that allows for studying numerous different vacation systems, including a.o. classical vacation systems like the exhaustive ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

عوامل تعیینکننده در انتخاب نرمافزار وبمحور معنایی در قالب یک سرویس:

چارچوبی یکپارچه در شرایط خرید الکترونیکی و برنامه ریزی منابع سرمایه ای

.png)

.png)

Abstract The ever increasing Internet bandwidth and the fast changing needs of businesses for effectiveness with the partners in the procurement chain and is leading organizations to adopt information systems infrastructures ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

طراحی و تحلیل یک مدل وقفه (تعطیلی) برای سیستم صف بندی دو فازه با خدمات ورودی

.png)

.png)

Abstract This paper mainly deals with a two phase service queueing model with gated service vacation. In this gated service vacation model, only those customers who are present in the queue ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

به اشتراک گذاری طیف مشارکتی بین شبکه های تلفن همراه و اد هاک

.png)

.png)

Abstract Spectrum sharing between cellular and ad-hoc networks is studied in this work. Weak signals and strong interferences at the cell-edge area usually cause severe performance degradation. To improve the cell-edge ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 139500 تومان

قیمت: 139500 تومان

قیمت: 139500 تومان

قیمت: 139500 تومان

مقایسه پروتکل های مسیر یابی تک مسیره در مقابل پروتکل های مسیر یابی چندگانه برای انتقال تصویر در شبکه های حسگر بی سیم چند رسانه ای

.png)

.png)

Abstract Wireless multimedia sensor network (WMSN) applications require strong multimedia communication competence. Therefore, in WMSN applications, it is necessary to use specific mechanisms in order to handle multimedia communication challenges and ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

هوش کسب و کار به روش محاسبه ابری

.png)

.png)

Abstract Business Intelligence (BI) deals with integrated approaches to management support. Currently, there are constraints to BI adoption and a new era of analytic data management for business intelligence these constraints ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

قیمت: 119500 تومان

مدل احتمال جدید برای ضمانت کردن مشکل مسیر بحرانی با الگوریتم اکتشافی

.png)

.png)

Abstract In order to obtain an adequate description of risk aversion for insuring critical path problem, this paper develops a new class of two-stage minimum risk problems. The first-stage objective function ... [ ادامه مطلب ]

انتشارات: ACM

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

قیمت: 129500 تومان

دستورالعمل طراحی و محاسبه سیستم روشنایی

.png)

.png)

مجموعه دستورالعمل های ارائه شده در دیتاسرا شامل ضوابط و مراحل تحلیل و طراحی سازه های گوناگون صنعتی و بر اساس الزامات مندرج در آیین نامه های معتبر داخلی و ... [ ادامه مطلب ]

قیمت: 119500 تومان

مشخصات کلی:

قیمت: 119500 تومان

مشخصات کلی:

صفحات متن اصلی: 30

گروه:

دستورالعمل طراحی

قیمت: 119500 تومان

قیمت: 119500 تومان

صفحات متن اصلی: 30

گروه: دستورالعمل طراحی

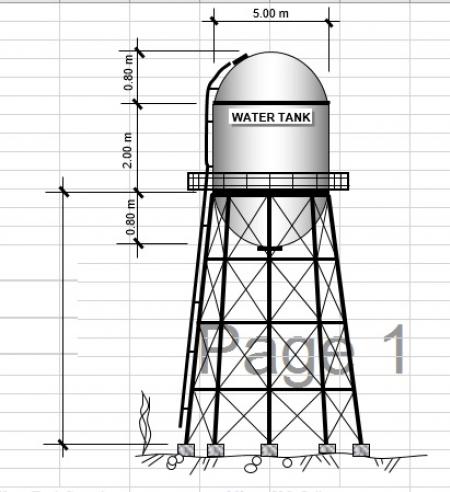

فایل اکسل طراحی مخزن فلزی هوایی بر اساس آیین نامه AISC با در نظر گرفتن نیروی باد و زلرله

.png)

.png)

فایل پیش رو اکسل طراحی مخزن فلزی هوایی می باشد که بر اساس آیین نامه AISC و با در نظر گرفتن نیروی باد و زلرله محاسبات را انجام داده و ... [ ادامه مطلب ]

قیمت: 79500 تومان

مشخصات کلی:

قیمت: 79500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 79500 تومان

قیمت: 79500 تومان

گروه: دستورالعمل طراحی

فایل اکسل تحلیل اتصال برشی دارای خروج از مرکزیت برای گروه پیچ

.png)

.png)

این برنامه ظرفیت برشی اتصال پیچ و مهره ای دارای خروج از مرکزیت برای گروه پیچ را محاسبه می کند، ابزاری مناسب برای طراحی صفحات gusset و اتصالات پیچ و ... [ ادامه مطلب ]

قیمت: 79500 تومان

مشخصات کلی:

قیمت: 79500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 79500 تومان

قیمت: 79500 تومان

گروه: دستورالعمل طراحی

فایل اکسل طراحی روسازی آسفالتی بر مبنای آیین نامه آشتو و استفاده از آزمایش ظرفیت باربری کالیفرنیا

.png)

.png)

فایل پیش رو اکسل طراحی روسازی آسفالتی بر مبنای آیین نامه آشتو می باشد که با استفاده از نتایج آزمایش ظرفیت باربری کالیفرنیا CBR اطلاعات ورودی را تحلیل و نتایج را ... [ ادامه مطلب ]

قیمت: 79500 تومان

مشخصات کلی:

قیمت: 79500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 79500 تومان

قیمت: 79500 تومان

گروه: دستورالعمل طراحی

دستورالعمل طراحی ابعاد و سازه شالوده های عمیق (شمع ها و پایه های عمیق) در خشکی

.png)

.png)

مجموعه دستورالعمل های ارائه شده در دیتاسرا شامل ضوابط و مراحل تحلیل و طراحی سازه های گوناگون صنعتی و بر اساس الزامات مندرج در آیین نامه های معتبر داخلی و ... [ ادامه مطلب ]

قیمت: 119500 تومان

مشخصات کلی:

قیمت: 119500 تومان

مشخصات کلی:

صفحات متن اصلی: 27

گروه:

دستورالعمل طراحی

قیمت: 119500 تومان

قیمت: 119500 تومان

صفحات متن اصلی: 27

گروه: دستورالعمل طراحی

تحلیل غیرخطی و مدل سازی عددی تیر بتن مسلح تقویت شده با FRP توسط Finite Element Method

.png)

.png)

"پایان نامه مهندسی عمران مقطع کارشناسی ارشد - گرایش سازه" تحلیل غیرخطی و مدل سازی عددی تیر بتن مسلح تقویت شده با FRP توسط Finite Element Method مشخصات کلی: شامل فایلهای word و ... [ ادامه مطلب ]

قیمت: 129500 تومان

مشخصات کلی:

قیمت: 129500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 129500 تومان

قیمت: 129500 تومان

گروه: دستورالعمل طراحی

بررسی پارامترهای هندسی مهاربند زانویی

.png)

.png)

"پروژه دانشجویی مهندسی عمران" بررسی پارامترهای هندسی مهاربند زانویی مشخصات کلی: شامل فایلهای word و pdf بالغ بر 146 صفحه (4 فصل) فهرست مطالب فصل اول 1-1- مقدمه 1-2- شکل پذیری سازه ها 1-3- مفصل و لنگر پلاستیک 1-4- منحنی ... [ ادامه مطلب ]

قیمت: 129500 تومان

مشخصات کلی:

قیمت: 129500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 129500 تومان

قیمت: 129500 تومان

گروه: دستورالعمل طراحی

تحلیل و طراحی سیستم گرمایشی ساختمان مسکونی با استفاده از ذخیره کننده های حرارتی PCM

.png)

.png)

"پایان نامه مهندسی مکانیک مقطع کارشناسی ارشد - گرایش تبدیل انرژی" تحلیل و طراحی سیستم گرمایشی ساختمان مسکونی با استفاده از ذخیره کننده های حرارتی PCM تهیه شده بصورت کاملا انحصاری توسط ... [ ادامه مطلب ]

قیمت: 449000 تومان

مشخصات کلی:

قیمت: 449000 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 449000 تومان

قیمت: 449000 تومان

گروه: دستورالعمل طراحی

شناسایی و رتبه بندی دلایل انحراف از هزینه پیش بینی شده و ارائه راهکارهای کاهش آن: مطالعه موردی پروژه های "پتروشیمی الف"

.png)

.png)

"پایان نامه مهندسی عمران مقطع کارشناسی ارشد - گرایش مهندسی و مدیریت ساخت" شناسایی و رتبه بندی دلایل انحراف از هزینه پیش بینی شده و ارائه راهکارهای کاهش آن: مطالعه ... [ ادامه مطلب ]

قیمت: 259500 تومان

مشخصات کلی:

قیمت: 259500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 259500 تومان

قیمت: 259500 تومان

گروه: دستورالعمل طراحی

مکانیک شکست (Fracture Mechanics)

.png)

.png)

مقدمه : یکی از عمده ترین مسائلی که انسان از زمان ساختن سادهترین ابزارها با آن مواجه بوده است پدیده شکست در اجسام میباشد و درواقع برای استفاده از مواد ... [ ادامه مطلب ]

قیمت: 99500 تومان

مشخصات کلی:

قیمت: 99500 تومان

مشخصات کلی:

گروه:

دستورالعمل طراحی

قیمت: 99500 تومان

قیمت: 99500 تومان

گروه: دستورالعمل طراحی

.png)